PowerEdge: AMD Rome — architektura i początkowa wydajność HPC

Summary: W dzisiejszym świecie HPC przedstawiamy najnowszą generację procesorów AMD EPYC o nazwie kodowej Rome.

Instructions

Garima Kochhar, Deepthi Cherlopalle, Joshua Weage. Laboratorium innowacji HPC i AI, październik 2019 r.

W dzisiejszym świecie HPC procesora AMD EPYC

Architektura

Rome to procesor AMD EPYC drugiej generacji, stanowiący modernizację procesora Naples pierwszej generacji.

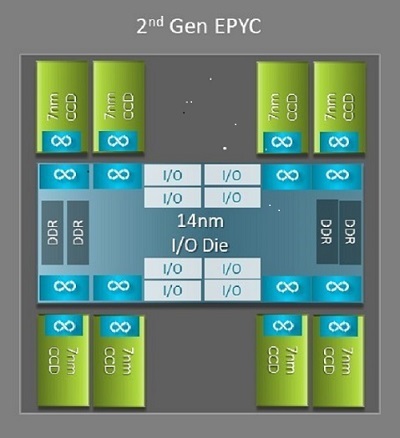

Jedną z największych różnic architektonicznych między procesorem Naples a procesorem Rome, która przynosi korzyści HPC, jest nowa matryca we/wy w procesorze Rome. W przypadku Rome każdy procesor jest pakietem wieloukładowym składającym się z maksymalnie dziewięciu chipletów, jak pokazano na rysunku 1. Istnieje jedna centralna matryca we/wy 14 nm, która zawiera wszystkie funkcje we/wy i pamięci – pomyśl o kontrolerach pamięci, łączach szkieletowych Infinity w gnieździe i łączności międzygniazdowej oraz PCI-e. W każdym gnieździe znajduje się osiem kontrolerów pamięci obsługujących osiem kanałów pamięci DDR4 z szybkością 3200 MT/s. Serwer jednogniazdowy może obsługiwać do 130 torów PCIe czwartej generacji. System z dwoma gniazdami może obsługiwać do 160 torów PCIe czwartej generacji.

(Rysunek 1. Pakiet wieloukładowy Rome z jedną centralną matrycą we/wy i matrycami maksymalnie ośmiordzeniowymi)

Wokół centralnej matrycy we/wy znajduje się do ośmiu chipletów rdzeniowych 7 nm. Chiplet rdzenia nazywany jest matrycą pamięci podręcznej rdzenia lub CCD. Każda matryca CCD ma rdzenie procesora oparte na mikroarchitekturze Zen2, pamięć podręczną L2 i 32 MB pamięci podręcznej L3. Sama matryca CCD dysponuje dwoma kompleksami pamięci podręcznej rdzenia (CCX),

(Rysunek 2. CCX z czterema rdzeniami i współużytkowaną pamięcią podręczną L3 o pojemności 16 MB)

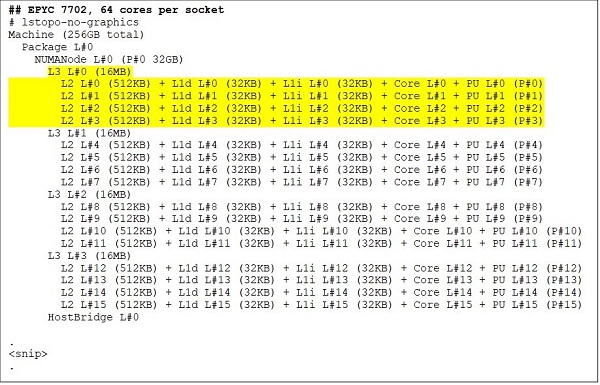

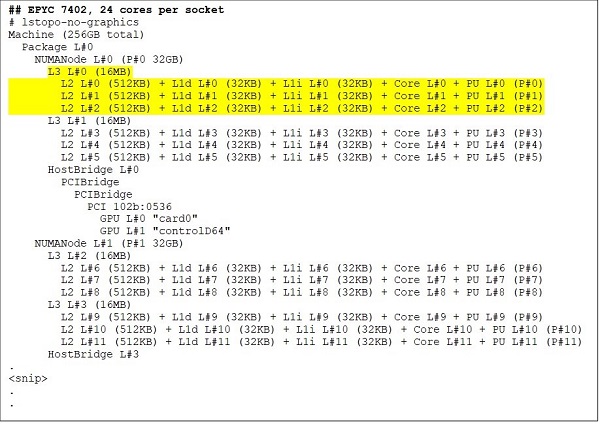

Różne modele procesorów Rome

Na najwyższym poziomie znajduje się model z 64-rdzeniowym procesorem, na przykład EPYC 7702. Dane wyjściowe narzędzia Lstopo pokazują, że ten procesor ma 16 CCX na gniazdo, każdy CCX ma cztery rdzenie, jak pokazano na rysunkach 3 i 4, co daje 64 rdzenie na gniazdo. 16 MB L3 na CCX, czyli 32 MB L3 na CCD daje temu procesorowi 256 MB pamięci podręcznej L3. Należy jednak pamiętać, że całkowita pamięć podręczna L3 w przypadku procesora Rome nie jest współdzielona przez wszystkie rdzenie. Pamięć podręczna L3 o pojemności 16 MB w każdym systemie CCX jest niezależna i współużytkowana tylko przez rdzenie w CCX, jak pokazano na rysunku 2.

24-rdzeniowy procesor, taki jak EPYC 7402, ma 128 MB pamięci podręcznej L3. Dane wyjściowe Lstopo na rysunkach 3 i 4 pokazują, że model ten ma trzy rdzenie na CCX i osiem rdzeni CCX na gniazdo.

(Rysunek 3 i 4. Dane wyjściowe narzędzia Lstopo dla procesorów 64-rdzeniowych i 24-rdzeniowych)

Bez względu na liczbę CCD, każdy procesor Rome jest logicznie podzielony na cztery kwadranty, przy czym CCD są rozmieszczone we wszystkich kwadrantach możliwie równomiernie oraz w każdym kwadrancie są dwa kanały pamięci. Centralna matryca we/wy może być traktowana jako logicznie obsługująca cztery kwadranty gniazda.

Opcje systemu BIOS oparte na architekturze Rome

Centralna matryca we/wy w procesorze Rome pomaga poprawić opóźnienia pamięci

Cztery kwadranty logiczne w procesorze Rome umożliwiają partycjonowanie procesora na różne domeny NUMA. Taka konfiguracja nosi nazwę NUMA na gniazdo lub NPS.

- NPS1 oznacza, że procesor Rome jest pojedynczą domeną NUMA ze wszystkimi rdzeniami w gnieździe i całą pamięcią w jednej domenie NUMA. Pamięć jest przeplatana przez osiem kanałów pamięci. Wszystkie urządzenia PCIe w gnieździe należą do jednej domeny NUMA

- NPS2 dzieli procesor na dwie domeny NUMA, z połową rdzeni i połową kanałów pamięci w gnieździe w każdej domenie NUMA. Pamięć jest przeplatana przez cztery kanały pamięci w każdej domenie NUMA

- NPS4 dzieli procesor na cztery domeny NUMA. Każdy kwadrant jest tutaj domeną NUMA, a pamięć jest przeplatana przez dwa kanały pamięci w każdym kwadrancie. Urządzenia PCIe są lokalne w jednej z czterech domen NUMA w gnieździe, w zależności od tego, który kwadrant matrycy we/wy zawiera rdzeń PCIe dla tego urządzenia

- Nie wszystkie procesory mogą obsługiwać wszystkie ustawienia serwera NPS

Serwer NPS4 jest zalecany do zastosowań HPC, ponieważ oczekuje się, że zapewni najlepszą przepustowość pamięci i najniższe opóźnienia pamięci, a nasze aplikacje zwykle obsługują technologię NUMA. Jeśli NPS4 nie jest dostępny, zalecamy najwyższy NPS obsługiwany przez model procesora — NPS2, a nawet NPS1.

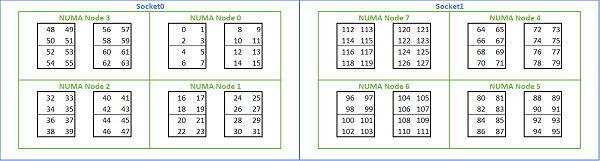

Biorąc pod uwagę dużą liczbę opcji NUMA dostępnych na platformach opartych na procesorach Rome, system BIOS PowerEdge umożliwia korzystanie z dwóch różnych metod wyliczania rdzeni w ramach wyliczania MADT. Wyliczenie liniowe numeruje rdzenie w kolejności, wypełniając jeden CCX, CCD, gniazdo przed przejściem do następnego gniazda. W przypadku procesora z 32 rdzeniami, rdzenie od 0 do 31 znajdują się w pierwszym gnieździe, a rdzenie 32–63 w drugim gnieździe. Wyliczenie algorytmu karuzelowego numeruje rdzenie we wszystkich regionach NUMA. W takim przypadku rdzenie parzyste znajdują się w pierwszym gnieździe, a nieparzyste w drugim. Dla uproszczenia zalecamy wyliczenie liniowe dla HPC. Na rysunku 5 przedstawiono przykład liniowego wyliczenia rdzeni na dwuprocesorowym serwerze z 64 rdzeniami skonfigurowanym w NPS4. Na rysunku każde pudełko z czterema rdzeniami to CCX, każdy zestaw ośmiu ciągłych rdzeni to CCD.

(Rysunek 5. Liniowe wyliczenie rdzeni w systemie z dwoma gniazdami, 64 rdzenie na gniazdo, konfiguracja NPS4 w modelu z ośmioma procesorami CCD)

Inna opcja systemu BIOS specyficzną dla procesorów Rome jest nazywana preferowanym urządzeniem we/wy. Jest to ważne urządzenie dostrajania przepustowości i szybkości komunikatów InfiniBand. Umożliwia platformie priorytetyzację ruchu dla jednego urządzenia we/wy. Ta opcja jest dostępna na platformach Rome z jednym i dwoma gniazdami procesorów, a urządzenie InfiniBand na danej platformie musi być wybrane jako preferowane urządzenie w menu BIOS, aby osiągnąć pełną szybkość komunikatów, gdy wszystkie rdzenie procesora są aktywne.

Podobnie jak w przypadku procesorów Naples, procesory Rome również obsługują wielowątkowośćlub procesor logiczny. W przypadku HPC pozostawiamy tę opcję wyłączoną, ale niektóre aplikacje mogą skorzystać z włączenia procesora logicznego. Zajrzyj do naszych kolejnych wpisów na blogu poświęconych badaniom nad zastosowaniami dynamiki molekularnej.

Podobnie jak w przypadku procesorów Naples, procesory Rome również pozwalają na CCX jako domenę NUMA. Ta opcja uwidacznia każdy CCX jako węzeł NUMA. W systemie z dwugniazdowymi procesorami z 16 CCX na procesor to ustawienie uwidacznia 32 domeny NUMA. W tym przykładzie każde gniazdo ma osiem CCD, czyli 16 CCX. Każdy CCX można włączyć jako własną domenę NUMA, co daje 16 węzłów NUMA na gniazdo i 32 w systemie dwugniazdowym. W przypadku HPC zalecamy pozostawienie CCX jako domeny NUMA w domyślnej opcji wyłączenia. Włączenie tej opcji powinno pomóc w środowiskach zwirtualizowanych.

Podobnie jak w przypadku procesorów Naples, procesory Rome pozwalają na ustawienie systemu w trybie determinizmu wydajności lub determinizmu mocy. W przypadku determinizmu wydajności system działa z częstotliwością oczekiwaną dla modelu procesora, zmniejszając zmienność między wieloma serwerami. W przypadku determinizmu mocy system działa z maksymalnym dostępnym TDP modelu procesora. Zwiększa to zmienność poszczególnych części w procesie produkcyjnym, dzięki czemu niektóre serwery są szybsze od innych. Wszystkie serwery mogą zużywać maksymalną moc znamionową procesora, co sprawia, że zużycie energii jest deterministyczne, ale pozwala na pewne różnice wydajności w przypadku wielu serwerów.

Jak można tego oczekiwać od platformy PowerEdge, system BIOS ma opcję meta o nazwie System Profile. Wybranie profilu systemu Performance-Optimized włącza tryb turbodoładowania, wyłącza stany C i ustawia suwak determinizmu na determinizm mocy, optymalizując go pod kątem wydajności.

Wyniki wydajności — mikrotesty STREAM, HPL, InfiniBand

Wielu z naszych czytelników mogło od razu przejść do tej części, więc przejdziemy od razu do rzeczy.

W Laboratorium Innowacji HPC i AI stworzyliśmy 64-serwerowy klaster o nazwie Minerva, oparty na procesorach Rome. Oprócz jednorodnego klastra Minerva, mamy kilka innych próbek procesorów Rome, które moglibyśmy ocenić. Nasze stanowisko testowe jest opisane w tabeli 1 i tabeli 2.

(Tabela 1 Modele procesorów Rome ocenione w tym badaniu)

| Procesor | Liczba rdzeni na gniazdo | Konfiguracja | Zegar bazowy | TDP |

|---|---|---|---|---|

| 7702 | 64c | 4 rdzenie na CCX | 2,0 GHz | 200W |

| 7502 | 32c | 4 rdzenie na CCX | 2,5 GHz | 180W |

| 7452 | 32c | 4 rdzenie na CCX | 2,35 GHz | 155W |

| 7402 | 24c | 3 rdzenie na CCX | 2,8 GHz | 180W |

(Tabela 2 Stanowisko testowe)

| Komponent | Szczegóły |

|---|---|

| Serwer | PowerEdge C6525 |

| Procesor | Jak pokazano w tabeli 1 z dwoma gniazdami |

| Pamięć | DDR4 256 GB, 16x16 GB, 3200 Mt/s |

| Połączenia | HDR100 ConnectX-6 Mellanox Infini Band |

| System operacyjny | Red Hat Enterprise Linux 7.6 |

| Jądro | 3.10.0.957.27.2.e17.x86_64 |

| Dysk twardy | Moduł M.2 SATA SSD 240 GB |

STREAM

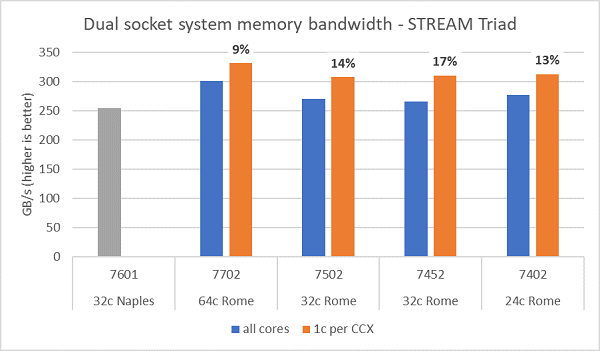

Testy przepustowości pamięci w przypadku procesorów Rome przedstawiono na rysunku 6, testy te zostały przeprowadzone w trybie NPS4. Zmierzyliśmy przepustowość pamięci ~270–300 GB/s na naszym dwugniazdowym serwerze PowerEdge C6525 przy użyciu wszystkich rdzeni serwera we wszystkich czterech modelach procesorów wymienionych w tabeli 1. Gdy używany jest tylko jeden rdzeń na CCX, przepustowość pamięci systemowej jest ~9-17% wyższa niż zmierzona dla wszystkich rdzeni.

Większość obciążeń roboczych HPC albo w pełni subskrybuje wszystkie rdzenie systemu, albo centra HPC działają w trybie wysokiej przepustowości z wieloma zadaniami na każdym serwerze. W związku z tym przepustowość pamięci dla wszystkich rdzeni jest dokładniejszym odzwierciedleniem przepustowości pamięci i przepustowości pamięci na rdzeń systemu.

Rysunek 6 przedstawia również przepustowość pamięci zmierzoną na platformie EPYC Naples poprzedniej generacji, która również obsługiwała osiem kanałów pamięci na gniazdo, ale działała z prędkością 2667 MT/s. Platforma Rome zapewnia od 5% do 19% lepszą całkowitą przepustowość pamięci niż Naples, a wynika to głównie z szybszej pamięci 3200 MT/s. Nawet przy 64 rdzeniach na gniazdo system Rome może dostarczyć ponad 2 GB/s/rdzeń.

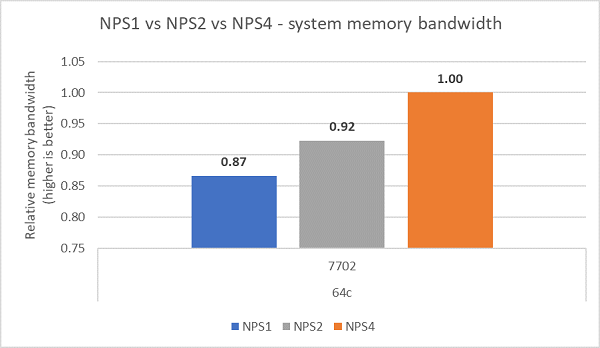

Porównując różne konfiguracje NPS, przy NPS4 zmierzono ~13% większą przepustowość pamięci w porównaniu z NPS1, jak pokazano na rysunku 7.

(Rysunek 6. Przepustowość dwugniazdowej pamięci NPS4 STREAM Triad)

(Rysunek 7. Przepustowość pamięci NPS1 w por. z NPS2 w por. z NPS 4)

Przepustowość i szybkość komunikatów InfiniBand

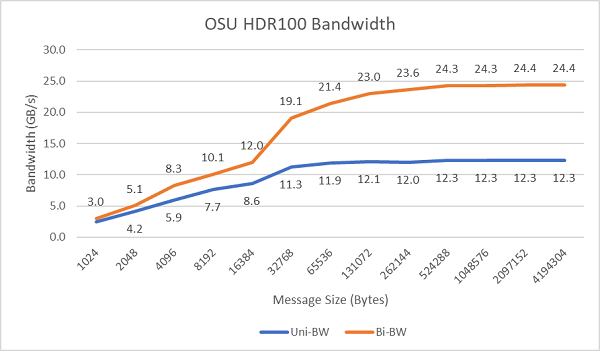

Rysunek 8 przedstawia przepustowość InfiniBand dla jednego rdzenia w przypadku testów jednokierunkowych i dwukierunkowych. Na stanowisku testowym użyto HDR100 działającego z szybkością 100 Gb/s, a wykres pokazuje oczekiwaną wydajność łącza dla tych testów.

Rysunek 8. Przepustowość InfiniBand (jeden rdzeń)

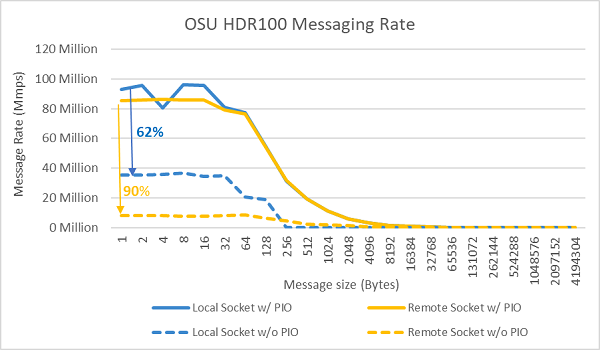

Rysunek 9. Szybkość komunikatów InfiniBand (wszystkie rdzenie)

Następnie przeprowadzono testy szybkości komunikatów przy użyciu wszystkich rdzeni gniazda na dwóch testowanych serwerach. Gdy preferowane urządzenie we/wy jest włączone w systemie BIOS, a karta ConnectX-6 HDR100 jest skonfigurowana jako urządzenie preferowane, szybkość komunikatów dla wszystkich rdzeni jest wyższa niż wtedy, gdy preferowane urządzenie we/wy nie jest włączone, jak pokazano na rysunku 9. Ilustruje to znaczenie tej opcji systemu BIOS podczas dostrajania pod kątem HPC, a zwłaszcza skalowalności aplikacji wielowęzłowych.

HPL

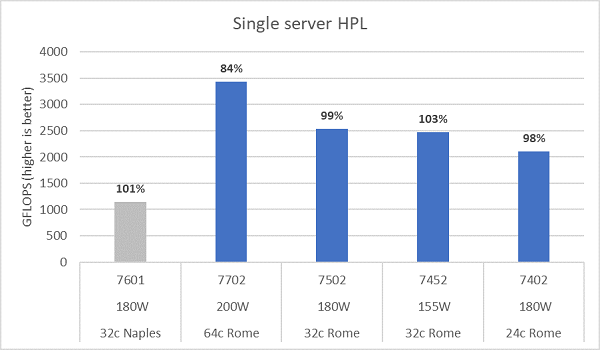

Mikroarchitektura Rome może wycofać 16 DP FLOP/cykl, dwa razy więcej niż procesor Naples, w przypadku którego ta wartość ta wynosiła 8 FLOPS/cykl. Daje to procesorowi Rome 4 razy więcej teoretycznych wartości szczytowych FLOPS w porównaniu z procesorem Naples, dzięki 2-krotnie większej zdolności do obliczeń zmiennoprzecinkowych i 2-krotnie większej liczbie rdzeni (64 rdzenie w porównaniu z 32 rdzeniami). Rysunek 10 przedstawia zmierzone wyniki HPL dla czterech testowanych przez nas modeli procesorów Rome wraz z naszymi poprzednimi wynikami z systemu opartego na procesorze Naples. Wydajność Rome HPL jest odnotowywana jako wartość procentowa nad słupkami na wykresie i jest wyższa dla modeli procesorów o niższym TDP.

Testy przeprowadzono w trybie determinizmu mocy, a ~5% różnicy wydajności zostało zmierzone na 64 identycznie skonfigurowanych serwerach, przez co wyniki w tym przypadku znajdują się w tym zakresie wydajności.

(Rysunek 10. HPL pojedynczego serwera w NPS4)

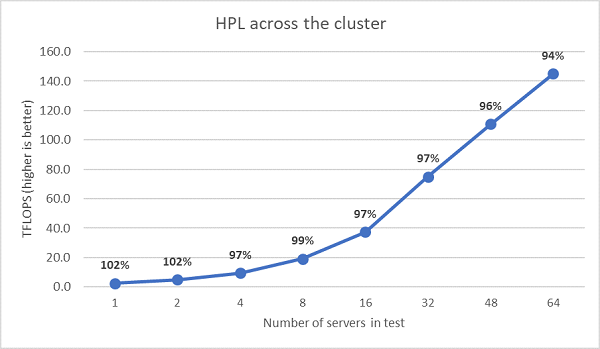

Następnie wykonano testy wielowęzłowego HPL, których wyniki przedstawiono na rysunku 11. Wydajność HPL dla EPYC 7452 utrzymuje się na poziomie powyżej 90% w skali 64-węzłowej, ale spadki wydajności ze 102% do 97% i wstecz do 99% wymagają dalszej oceny.

(Rysunek 11. Wielowęzłowy HPL, dwugniazdowy procesor EPYC 7452 na InfiniBand HDR100)

Podsumowanie i dalszy ciąg:

Wstępne badania wydajności serwerów opartych na procesorach Rome wykazały oczekiwaną wydajność naszego pierwszego zestawu testów porównawczych HPC. Dostrajanie systemu BIOS jest ważne podczas konfigurowania w celu uzyskania najlepszej wydajności, a opcje dostrajania są dostępne w naszym profilu obciążenia roboczego HPC systemu BIOS, który można skonfigurować fabrycznie lub ustawić za pomocą narzędzi do zarządzania systemami Dell EMC.

Laboratorium innowacji HPC i AI