AMD Rome - це реально? Архітектура та початкова продуктивність HPC

Summary: Сьогодні у світі HPC знайомство з процесором AMD EPYC останнього покоління під кодовою назвою Rome.

Symptoms

Гаріма Кочхар, Діпті Черлопалле, Джошуа Веейдж. HPC та AI Innovation Lab, жовтень 2019 р.

Cause

Не застосовується

Resolution

Сьогодні у світі HPC процесор AMD EPYC  останнього покоління під кодовою назвою Rome навряд чи потребує представлення. Останні кілька місяців ми оцінювали системи на базі Риму в лабораторії HPC та AI Innovation Lab , а нещодавно Dell Technologies анонсувала

останнього покоління під кодовою назвою Rome навряд чи потребує представлення. Останні кілька місяців ми оцінювали системи на базі Риму в лабораторії HPC та AI Innovation Lab , а нещодавно Dell Technologies анонсувала  сервери, які підтримують цю архітектуру процесорів. У цьому першому блозі з серії Rome обговорюється архітектура процесорів Rome, як її можна налаштувати для продуктивності HPC і представити початкову продуктивність мікро-еталонів. У подальших блогах описується продуктивність додатків у сферах CFD, CAE, молекулярної динаміки, моделювання погоди та інших застосувань.

сервери, які підтримують цю архітектуру процесорів. У цьому першому блозі з серії Rome обговорюється архітектура процесорів Rome, як її можна налаштувати для продуктивності HPC і представити початкову продуктивність мікро-еталонів. У подальших блогах описується продуктивність додатків у сферах CFD, CAE, молекулярної динаміки, моделювання погоди та інших застосувань.

Архітектура

Rome – це процесор EPYC 2-го покоління від AMD, який оновлює Naple 1-го покоління.

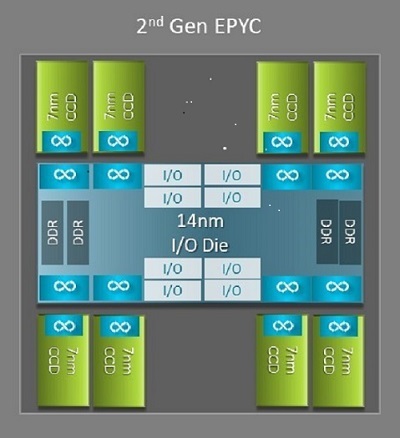

Однією з найбільших архітектурних відмінностей між Неаполем і Римом, яка приносить користь HPC, є новий матриця IO в Римі. У Римі кожен процесор являє собою багатокристальний пакет, що складається до 9 чиплетів , як показано на рис.1. Є один центральний 14-нм кристал вводу-виводу, який містить усі функції вводу-виводу та пам'яті - згадайте контролери пам'яті, ланки тканини Infinity всередині сокета та міжсокетного підключення, а також PCI-e. На роз'єм припадає вісім контролерів пам'яті, які підтримують вісім каналів пам'яті під управлінням DDR4 зі швидкістю 3200 МТ/с. Односокетний сервер може підтримувати до 130 ліній PCIe Gen4. Двосокетна система може підтримувати до 160 ліній PCIe Gen4.

(Рис.1Римський багатокристальний корпус з одним центральним кристалом вводу-виводу та до восьмиядерних кристалів)

Навколо центрального кристала вводу-виводу розташовано до восьми 7-нм сердечних чиплетів. Чиплет ядра називається кристалом Core Cache або CCD. Кожен CCD має ядра процесора на основі мікроархітектури Zen2, кеш-пам'ять L2 та 32 МБ кеш-пам'яті L3. Сам CCD має два комплекси Core Cache Complex (CCX), кожен CCX має до чотирьох ядер і 16 МБ кеш-пам'яті L3. На малюнку 2 показана ССХ.

кожен CCX має до чотирьох ядер і 16 МБ кеш-пам'яті L3. На малюнку 2 показана ССХ.

(Малюнок.2 : CCX з чотирма ядрами та спільним кешем L3 16 МБ)

Різні моделі  процесорів Rome мають різну кількість ядер,

процесорів Rome мають різну кількість ядер, але всі вони мають один центральний кристал вводу-виводу.

але всі вони мають один центральний кристал вводу-виводу.

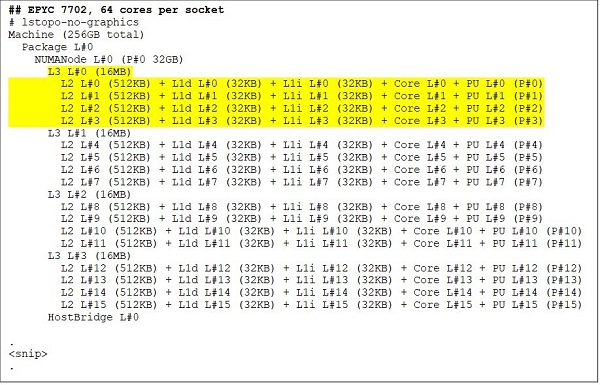

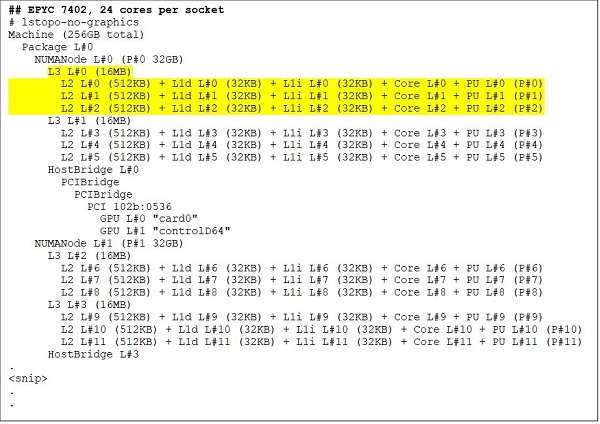

На верхньому торці знаходиться 64-ядерна модель процесора, наприклад, EPYC 7702. Вихід Lstopo показує нам, що цей процесор має 16 CCX на сокет, кожен CCX має чотири ядра, як показано на рисунках 3 і 4, таким чином дає 64 ядра на сокет. 16 МБ L3 на CCX, тобто 32 МБ L3 на CCD, дає цьому процесору загалом 256 МБ кеш-пам'яті L3. Однак зауважте, що загальний кеш L3 у Римі не використовується для всіх ядер. Кеш L3 розміром 16 МБ у кожному CCX є незалежним і використовується лише для ядер у CCX, як показано на малюнку 2.

24-ядерний процесор, такий як EPYC 7402, має 128 МБ кеш-пам'яті L3. Вихід Lstopo на рисунках 3 і 4 ілюструє, що ця модель має три ядра на CCX і 8 CCX на сокет.

(Рис.3 і 4 lstopo вихід для 64-ядерних і 24-ядерних процесорів)

Незалежно від кількості CCD, кожен римський процесор логічно розділений на чотири квадранти з CCD, розподіленими максимально рівномірно по квадрантах, і двома каналами пам'яті в кожному квадранті. Центральний кристал вводу-виводу можна розглядати як логічно підтримує чотири квадранти гнізда.

Опції BIOS на основі архітектури Rome

Центральний кристал IO в Римі допомагає зменшити затримки  пам'яті в порівнянні з тими, що були виміряні в Неаполі. Крім того, це дозволяє налаштувати процесор як єдиний домен NUMA, що забезпечує рівномірний доступ до пам'яті для всіх ядер у сокеті. Про це йдеться нижче.

пам'яті в порівнянні з тими, що були виміряні в Неаполі. Крім того, це дозволяє налаштувати процесор як єдиний домен NUMA, що забезпечує рівномірний доступ до пам'яті для всіх ядер у сокеті. Про це йдеться нижче.

Чотири логічні квадранти в римському процесорі дозволяють розділити центральний процесор на різні домени NUMA. Цей параметр називається NUMA per socket або NPS.

- NPS1 має на увазі, що процесор Rome є єдиним доменом NUMA, з усіма ядрами в сокеті та всією пам'яттю в цьому одному домені NUMA. Пам'ять чергується між собою вісьмома каналами пам'яті. Усі пристрої PCIe на сокеті належать до цього єдиного домену NUMA

- NPS2 розділяє процесор на два домени NUMA, з половиною ядер і половиною каналів пам'яті на сокеті в кожному домені NUMA. Пам'ять чергується між чотирма каналами пам'яті в кожному домені NUMA

- NPS4 розділяє центральний процесор на чотири домени NUMA. Кожен квадрант тут є доменом NUMA, і пам'ять чергується між двома каналами пам'яті в кожному квадранті. Пристрої PCIe є локальними для одного з чотирьох доменів NUMA на сокеті залежно від того, який квадрант кристала вводу-виводу має кореневий вміст PCIe для цього пристрою

- Не всі процесори можуть підтримувати всі налаштування NPS

Там, де це можливо, NPS4 рекомендується для HPC, оскільки очікується, що він забезпечить найкращу пропускну здатність пам'яті, найменші затримки пам'яті, а наші програми, як правило, враховують NUMA. Там, де NPS4 недоступний, ми рекомендуємо використовувати найвищий NPS, що підтримується моделлю CPU - NPS2, або навіть NPS1.

З огляду на безліч опцій NUMA, доступних на платформах, розташованих у Римі, BIOS PowerEdge дозволяє два різні методи нумерації ядер під нумерацією MADT. Лінійний перебір нумерації ядер по порядку, заповнюючи один CCX, CCD, роз'єм перед переходом до наступного розетки. На процесорі 32c ядра від 0 до 31 будуть на першому сокеті, ядра 32-63 на другому роз'ємі. Круговий перелік нумерує ядра в різних регіонах NUMA. При цьому на першому гнізді знаходяться парні жили, на другому - непарні. Для простоти ми рекомендуємо лінійне перерахування для HPC. На рис.5 наведено приклад лінійного перебору ядер на двосокетному сервері 64c, налаштованому в NPS4. На малюнку кожна коробка з чотирьох жил є CCX, кожен набір з восьми суміжних жил є CCD.

(Рис.5 Лінійне нумерація ядер на системі з двома сокетами, 64c на сокет, конфігурація NPS4 на моделі процесора 8 CCD)

Ще одна опція BIOS, характерна для Риму, називається Preferred IO Device. Це важлива ручка налаштування пропускної здатності та швидкості повідомлень InfiniBand. Це дозволяє платформі визначати пріоритетність трафіку для одного пристрою вводу-виводу. Ця опція доступна на платформах Rome з одним і двома сокетами, і пристрій InfiniBand на платформі необхідно вибрати як кращий пристрій у меню BIOS, щоб досягти повної частоти повідомлень, коли всі ядра процесора активні.

Подібно до Неаполя, Рим також підтримує гіперпоточністьабо логічний процесор. Для HPC ми залишаємо це вимкненим, але деякі програми можуть отримати вигоду від увімкнення логічного процесора. Шукайте наші подальші блоги, присвячені дослідженням застосування молекулярної динаміки.

Подібно до Неаполя, Рим також дозволяє CCX як домен NUMA. Цей параметр відображає кожен CCX як вузол NUMA. У системі з двосокетними процесорами та 16 CCX на процесор цей параметр відкриває 32 домени NUMA. У цьому прикладі кожен сокет має 8 CCD, тобто 16 CCX. Кожен CCX може бути включений як окремий домен NUMA, що дає 16 вузлів NUMA на сокет і 32 в системі з двома сокетами. Для HPC ми рекомендуємо залишити CCX як домен NUMA з опцією за замовчуванням вимкнено. Очікується, що увімкнення цієї опції допоможе віртуалізованим середовищам.

Подібно до Неаполя, Рим дозволяє встановити систему в режим детермінізму продуктивності або детермінізму сили . Згідно з детермінізмом продуктивності, система працює на очікуваній частоті для моделі процесора, зменшуючи варіативність на декількох серверах. У енергетичному детермінізмі система працює на максимально доступному TDP моделі CPU. Це посилює варіації від частини до частини у виробничому процесі, дозволяючи деяким серверам працювати швидше, ніж інші. Усі сервери можуть споживати максимальну номінальну потужність центрального процесора, що робить споживання енергії детермінованим, але допускає деякі варіації продуктивності на кількох серверах.

Як і слід було очікувати від платформ PowerEdge, BIOS має мета-опцію під назвою «Системний профіль». Вибір системного профілю «Оптимізована продуктивність » вмикає режим турбонаддуву, вимикає C-стани та встановлює повзунок детермінізму на «Детермінізм потужності», оптимізуючи для продуктивності.

Результати продуктивності - мікробенчмарки STREAM, HPL, InfiniBand

Багато наших читачів, можливо, відразу перейшли до цього розділу, тому ми зануримося в нього.

У лабораторії інновацій HPC та AI ми створили кластер із 64 серверами в Римі, який ми називаємо Minerva. На додаток до гомогенного кластера Minerva, у нас є кілька інших зразків процесорів Rome, які ми могли б оцінити. Наш тестовий стенд описаний в Таблиці 1 і Таблиці 2.

(Таблиця 1: Римські моделі процесорів, оцінені в цьому дослідженні)

| ЦП | Кількість ядер на розетку | Конфігурація | Базовий годинник | ТДП |

|---|---|---|---|---|

| 7702 | 64 С | 4c на CCX | 2,0 ГГц | 200 Вт |

| 7502 | 32 С | 4c на CCX | 2,5 ГГц | 180 Вт |

| 7452 | 32 С | 4c на CCX | 2,35 ГГц | 155 Вт |

| 7402 | 24 С | 3 с на ССХ | 2,8 ГГц | 180 Вт |

(Табл.2 Випробувальний стенд)

| Компонент | Деталі |

|---|---|

| Сервер | PowerEdge C6525 |

| Процесор | Як показано в таблиці.1, дворозеткові |

| Пам'ять | 256 ГБ, 16x16 ГБ 3200 МТ/с DDR4 |

| З'єднання | ConnectX-6 Mellanox Infini Band HDR100 |

| Операційна система | Red Hat Enterprise Linux 7.6 |

| Ядра | 3.10.0.957.27.2.e17.x86_64 |

| Диск | Модуль SSD M.2 SATA 240 ГБ |

ПОТІК

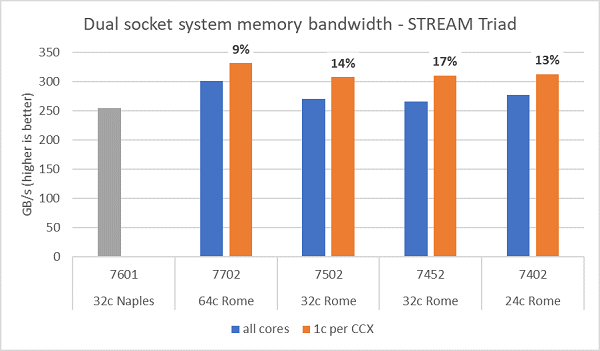

Тести пропускної здатності пам'яті на Rome представлені на рис.6, ці тести проводилися в режимі NPS4. Ми виміряли пропускну здатність пам'яті ~270-300 ГБ/с на нашому двосокетному PowerEdge C6525 при використанні всіх ядер сервера в чотирьох моделях процесорів, перелічених у таблиці.1. Коли на CCX використовується лише одне ядро, пропускна здатність системної пам'яті на ~9-17% вища, ніж виміряна з усіма ядрами.

Більшість робочих навантажень HPC або повністю підписуються на всі ядра системи, або центри HPC працюють у режимі високої пропускної здатності з кількома завданнями на кожному сервері. Отже, пропускна здатність всеядерної пам'яті є більш точним відображенням пропускної здатності пам'яті та можливостей пропускної здатності пам'яті на ядро системи.

На малюнку 6 також показана пропускна здатність пам'яті, виміряна на платформі попереднього покоління EPYC Naples , яка також підтримувала вісім каналів пам'яті на сокет, але працювала зі швидкістю 2667 МТ/с. Платформа Rome забезпечує від 5% до 19% кращу загальну пропускну здатність пам'яті, ніж Неаполь, і це в основному пов'язано з більш швидкою пам'яттю 3200 МТ/с. Навіть з 64c на сокет, система Rome може видавати до 2 ГБ/с/ядро.

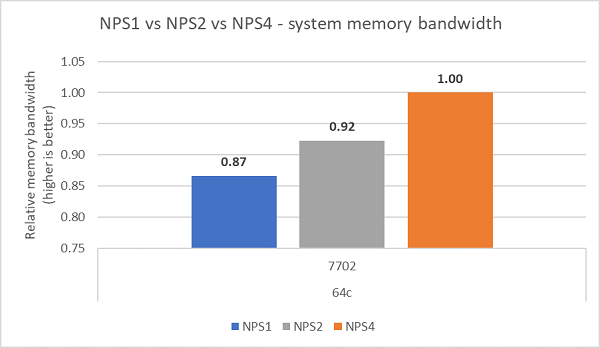

Порівнюючи різну конфігурацію NPS, було виміряно на ~13% вищу пропускну здатність пам'яті з NPS4 порівняно з NPS1, як показано на рисунку 7.

(Рис.6 Пропускна здатність пам'яті Dual-socket NPS4 STREAM Triad)

(Рис.7 NPS1 проти NPS2 проти NPS 4 Пропускна здатність пам'яті)

Пропускна здатність InfiniBand і швидкість повідомлень

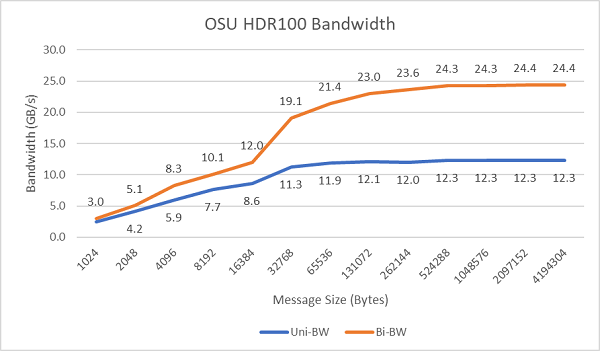

На малюнку 8 показана одноядерна смуга пропускання InfiniBand для односпрямованих і двонаправлених тестів. На тестовому стенді використовувався HDR100, що працює на швидкості 100 Гбіт/с, і графік показує очікувану продуктивність лінійної частоти для цих тестів.

Рис.8 Пропускна здатність InfiniBand (одноядерна))

Рис.9 Швидкість повідомлень InfiniBand (всі ядра))

Далі були проведені тести швидкості обміну повідомленнями з використанням усіх ядер на сокеті на двох протестованих серверах. Коли в BIOS увімкнено бажаний вводу-вивід, а адаптер ConnectX-6 HDR100 налаштований як бажаний пристрій, частота повідомлень на всіх ядрах значно вища, ніж коли не ввімкнено вводу-виводу-виводу, як показано на малюнку 9. Це ілюструє важливість цієї опції BIOS під час налаштування для HPC і особливо для масштабованості багатовузлових програм.

HPL

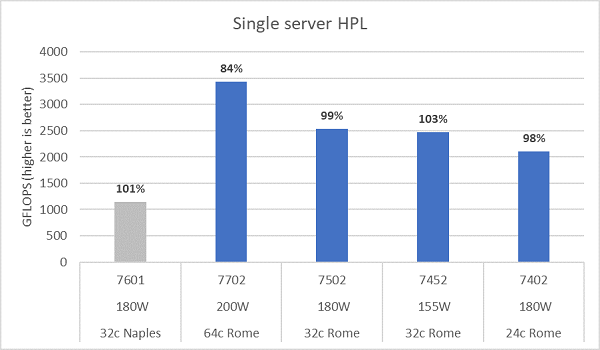

Римська мікроархітектура може виводити з ладу 16 DP FLOP/цикл, що вдвічі більше, ніж у Неаполі, який становив 8 FLOPS/цикл. Це дає Риму в 4 рази більше теоретичного піку FLOPS над Неаполем, у 2 рази завдяки покращеній можливості плаваючої комірки та в 2 рази більшій кількості ядер (64c проти 32c). На малюнку 10 показані результати вимірювання HPL для чотирьох протестованих нами моделей процесорів Rome, а також наші попередні результати з системи в Неаполі. Ефективність Rome HPL відзначається як відсоткове значення над стовпчиками на графіку і є вищою для моделей процесорів з нижчим TDP.

Тести проводилися в режимі Power Determinism, і було виміряно ~5% дельту продуктивності на 64 серверах з однаковою конфігурацією, результати тут, таким чином, знаходяться в цьому діапазоні продуктивності.

(Рис.10 Односерверний HPL в NPS4)

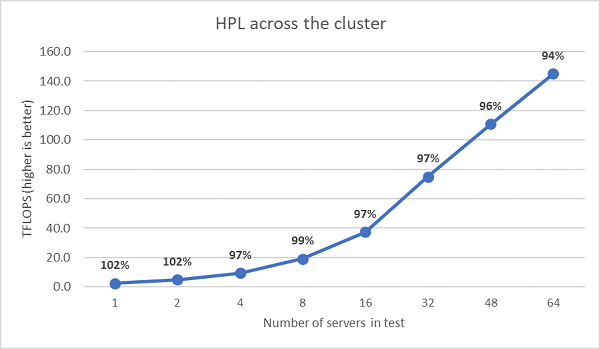

Були проведені наступні багатовузлові HPL-тести, і ці результати відображені на рис.11. Ефективність HPL для EPYC 7452 залишається вище 90% на 64-вузловому рівні, але падіння ефективності зі 102% до 97% і назад до 99% потребує подальшої оцінки.

(Рис.11 Багатовузловий HPL, двороз'ємний EPYC 7452 через HDR100 InfiniBand)

Підсумки і що буде далі

Початкові дослідження продуктивності серверів, розташованих у Римі, показують очікувану продуктивність для нашого першого набору тестів HPC. Налаштування BIOS важливе під час налаштування для найкращої продуктивності, і параметри налаштування доступні в нашому профілі робочого навантаження BIOS HPC, який можна налаштувати на заводі або встановити за допомогою утиліт керування системами Dell EMC.

HPC та AI Innovation Lab мають новий кластер PowerEdge Minerva на 64 сервери, що базується в Римі. Слідкуйте за наступними блогами, які описують дослідження продуктивності додатків на нашому новому кластері Minerva.